# of Direct Tunneling Current during Behavioral Synthesis of Nanometer CMOS Circuits

# Saraju P. Mohanty, Valmiki Mukherjee and Ramakrishna Velagapudi

Dept of Computer Science and Engineering

University of North Texas

Email: smohanty@cs.unt.edu

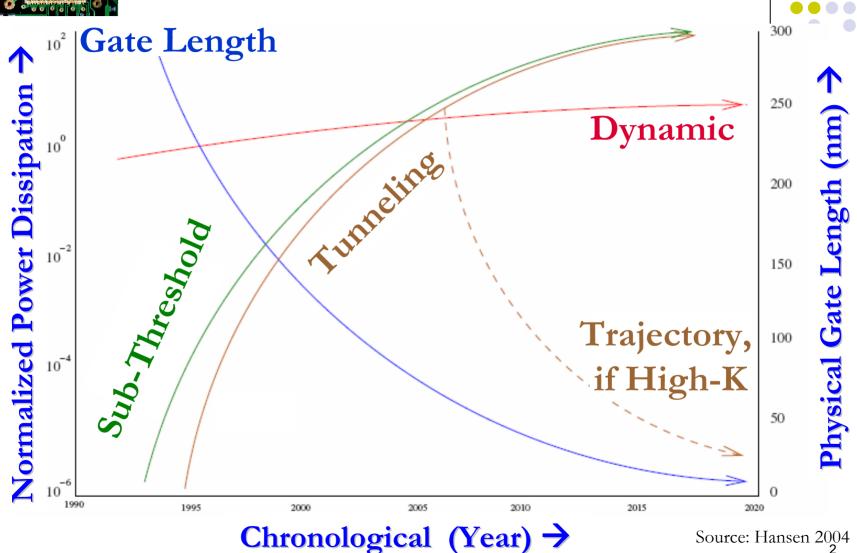

## **Power Dissipation Trend**

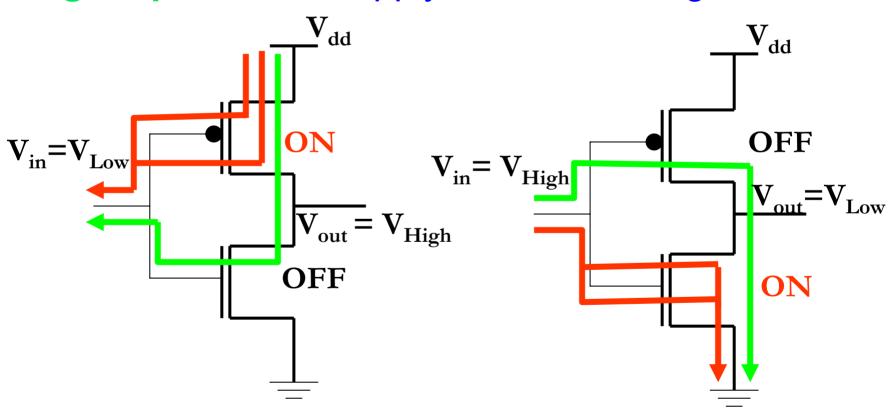

# unneling Paths in an Inverte

- Low Input: Input supply feeds tunneling current.

- High Input: Gate supply feeds tunneling current.

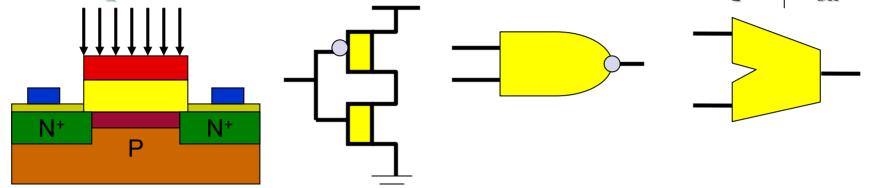

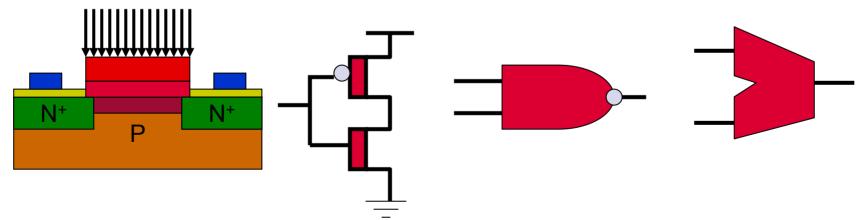

## Dual-T<sub>OX</sub>?

Gate oxide tunneling current I<sub>ox</sub> [Kim2003, Chandrakasan2001] (α is an experimentally derived factor):

$$I_{ox} \propto (V_{dd} / T_{ox})^2 \exp(-\alpha T_{ox} / V_{dd})$$

- Options for reduction of tunneling current :

- Decreasing of supply voltage V<sub>dd</sub> (will play its role)

- Increasing gate SiO<sub>2</sub> thickness T<sub>ox</sub> (delay increases)

- We believe that combined use of high-T<sub>ox</sub> resources and low-T<sub>ox</sub> resources can reduce the gate oxide tunneling current of a datapath with little compromise in circuit performance.

# Dual-T<sub>ox</sub>?

Assumption: All transistors of a resource are of equal To

High T<sub>ox</sub> Resource : Smaller I<sub>ox</sub>, but Larger delay

Low T<sub>ox</sub> Resource : Larger I<sub>ox</sub>, but Smaller delay

#### Related Works

#### **Behavioral Level Subthreshold:**

- Khouri, TVLSI 2002: Algorithms for subthreshold leakage power analysis and reduction using dual threshold voltage.

- Gopalakrishnan, ICCD2003 : MTCMOS approach for reduction of subthreshold current

#### Logic / Transistor Level Tunneling:

- Lee, TVLSI2004: Pin reordering to minimize gate leakage during standby positions of NOR and NAND gates.

- Sultania, DAC2004: Heuristic for dual T<sub>ox</sub> assignment for tunneling current and delay tradeoff.

# ical Model for Tunneling Curre

- We assumed that resources such as adders, subtractors, multipliers, dividers, are constructed using 2-input NAND.

- There are total n<sub>total</sub> NAND gates in the network of NAND gates constituting a n-bit functional unit.

- n<sub>cp</sub> number of NAND gates are in the critical path.

# ical Model for Tunneling Curren

• The tunneling current of a n-bit functional unit !:

$$I_{DTFU} = \sum_{j = (1 \rightarrow ntotal)} Pr_j \sum_{MOSi \epsilon NANDj} Pr_i I_{DTi}$$

$Pr_j$  is the probability that input of the NAND gate is at logic "0", and  $Pr_j$  is the probability that inputs of the transistors that are connected in the parallel i.e. PMOS are at logic "0".

• The average tunneling current for a NAND is calculated as  $I_{DTNAND} = \sum_{MOSi \ \epsilon \ NAND} Pr_i I_{DTi}$

# cal Model for Tunneling Current

The direct tunneling current of a MOS :

$$I_{DT} = \frac{WLq^{3}V_{ox}^{2}}{16\pi^{2}\phi_{B}T_{ox}^{2}} \exp\left[-\frac{4\sqrt{2m_{eff}}\phi_{B}^{1.5}T_{ox}}{3\hbar qV_{ox}}\left\{1 - \left(1 - \frac{V_{ox}}{\phi_{B}}\right)^{1.5}\right\}\right]$$

• The voltage across the MOSFET gate dielectric  $V_{ox}$  is expressed as follows:

$$V_{ox} = V_{gs} - V_{fb} - \Psi_{S} - V_{poly}$$

# cal Model for Tunneling Current

• By solving a quadratic equation we obtain an expression for  $V_{ox}$ .

$$V_{OX} = \frac{\sqrt{1 - 2(V_{fb} + \psi_{S} - V_{gs})(\frac{\varepsilon_{OX}^{2}}{q\varepsilon_{Si}N_{poly}T_{OX}^{2}}) - 1}}{(\frac{\varepsilon_{OX}^{2}}{q\varepsilon_{Si}N_{poly}T_{OX}^{2}})}$$

- The flat-band voltage  $V_{fb}$  can be obtained using the expression  $(qN_{channel}T^2_{ox}/2\epsilon_{Si})$ .

- $\Psi_S$  = 2 \* Fermi-Level, for strong inversion.

## cal Model for Propagation Details

• The critical path delay of a *n* bit functional unit using the NAND gates as building blocks:

$$Tpd_{FU} = \sum_{I=(1 \rightarrow ncp)} 0.5(n_{fan-in}Tpd_{NMOS} + Tpd_{PMOS})$$

- n<sub>fan-in</sub> is the effective fan-in factor.

- Using physical-alpha-power model the delay of a MOS, where  $I_{DSat0}$  is the saturation drain current of the MOS for  $V_{as} = V_{dd}$ .

current of the MOS for

$$V_{gs} = V_{dd}$$

$$T_{pd} = \frac{0.5 C_L V_{dd}}{I_{DSat 0}} + T_T \begin{cases} \frac{gs}{0.5 - (\frac{V_{dd}^{dd} - V_{Th}}{V_{dd}})}{\alpha + 1} \end{cases}$$

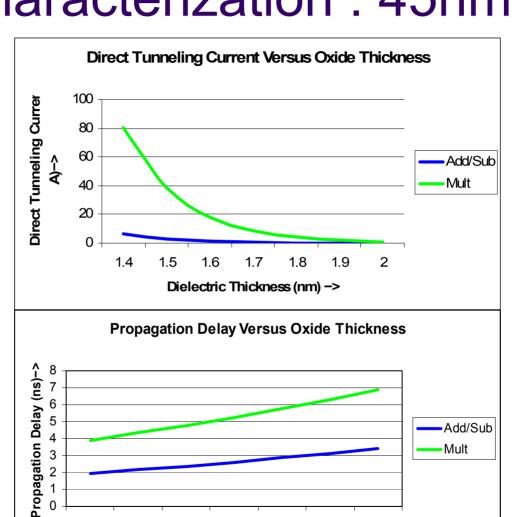

## Characterization: 45nm Tec

1.4

1.5

1.6

1.7

Dielectric Thickness (nm) ->

1.8

1.9

2

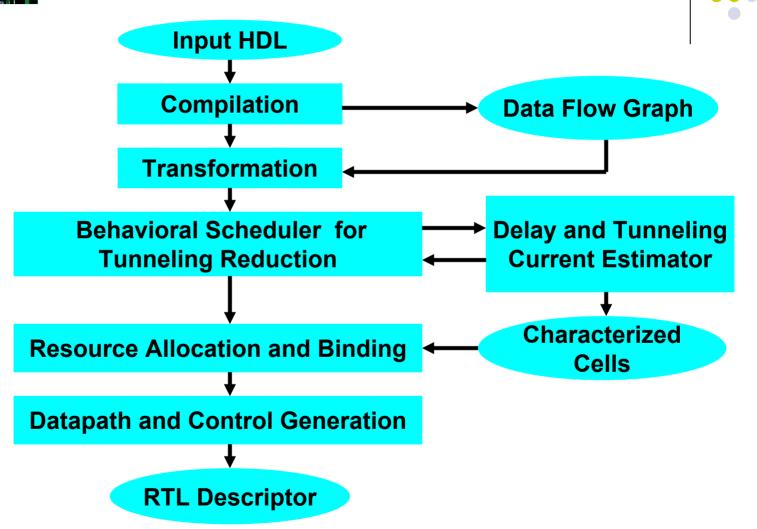

# Based Behavioral Synthe

# Dual-T<sub>ox</sub> Assignment : Basis

- Observation: Tunneling current of Functional Units increases and propagation delay decreases as oxide thickness deceases.

- Strategy: Maximize utilization of high-T<sub>OX</sub> high leaky resources (e. g. multipliers) and low-T<sub>ox</sub> low leaky resources (e.g. adder-subtractor) to improve chances of tunneling current reduction with minimal performance degradation.

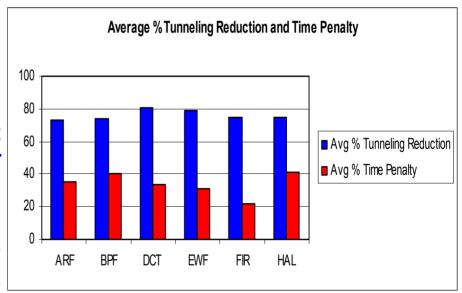

### **Experimental Results**

- The library consists of Multipliers and Adder-Subractor units, characterized for the 45 nm technology.

- We used T<sub>1</sub> = 1.4 nm, and T<sub>2</sub>

= 1.7 nm to perform our experiments.

- The value of T<sub>1</sub> is chosen as the default value from the BSIM4.4.0 model card and value of T<sub>2</sub> is intuitively chosen.

#### bnclusions and Future Works

- Tunneling current is a major component of total power consumption of a low-end CMOS nanometer circuit.

- Dual-T<sub>OX</sub> approach results significant reductions in tunneling current with minimal performance penalty.

- Development of optimal assignment algorithm is under progress.

- Tradeoff of tunneling, area and performance needs to be explored.

- Dual-T<sub>OX</sub> based design may need more masks for the lithographic process during fabrication.